XPRESS 2.0 VI

DATASHEET Rev. 2

# GENIE-PCIe2™

# PCI EXPRESS 2.0 VERIFICATION IP

# OVERVIEW

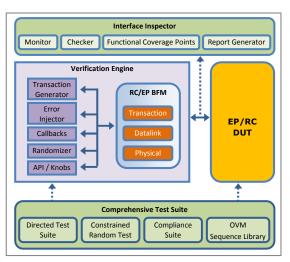

The Genie-PCIe2<sup>™</sup> Verification IP Products provide the most robust verification solution for PCIe 2.0 based designs. The intelligent **Verification Engine**, advanced **Interface Inspector** and comprehensive **Compliance Suite** provide the Perfect combination of tools to reduce design risk, verification time and project costs. Genie-PCIe<sup>™</sup>

The **Genie-PCIe2<sup>™</sup> VIP** provides a quick and efficient way to verify any PCIe based design – Root Complex, End Point or Switch. It supports the PCIe 2.0 specification and is backwards compatible with PCIe 1.1 and 1.0a specification addressing all layers of the PCIe protocol – Phy, Datalink, Transaction layer and Configuration Space. Genie-PCIe provides a complete verification solution that includes multi-language support and OVM methodology.

Fig. 1: Simple RC/EP Design

Fig. 2: PCIe Switch Design

Link width support: x1, x2, x4, x8, x12, x16,

Full LTSSM (Link Training & Status) support

Complete Configurable Order Management

Automatic /user configurable handling of all

Automatic /user configurable generation of

Supports transaction-oriented request-

based on address and command type

Checks all TLPs for correct formation of

memory space and message transfers

Supports Error Injection at all layers

Supports OVM/UVM/VMM methodology

headers, prefixes and ECRC

completion and error injection sequences

Generates block read and write transfers to

flow control packets and credit management

Full Requester and Completer functions

| The Genie-PCIe VI | P provides: |

|-------------------|-------------|

|-------------------|-------------|

- Bus Functional Models

- Directed and Random Transaction Generator

- Packet & Order set Generator

- Error Injector

- Callbacks

- Monitor/Checker

- Report Generator

# **FEATURES**

- Compliant with PCI Express Specification v2.0, v1.1 and 1.0a

Supports Gen 1, 2, 8b/10b encoding

Supports up to 8 virtual channels

Verification at PIPE (8 /16/32 bit), 10b, and serial interface

Configurable TS1, TS2, SKP Ordered set generation

Supports randomization for packet fields and data payload with or without error injection

Robust BFM API automates sending TLPs/DLLPs and controlling automatic BFM device response behaviour and link and device state transitions

- Full DL state machines and configurable ACK/NACK and Replay timers

- Provides read and write transfers to memory, I/O, and configuration space

- Language Interface SystemVerilog & Verilog

Comprehensive Compliance Suite PCI-SIG

- Supports Performance evaluations like

- Supports Performance evaluations like bandwidth, utilization, efficiency calculations

x32

loaic

layer packets

attributes

÷.

÷.

•••

÷.

### PRODUCT DETAILS

#### **Single-Link Operation**

In the single-link mode, the BFM is configured as a single link supporting x1, x2, x4, x8, x12, x16 or x32 operation. The BFM is enriched with Knobs to provide complete configurability over packet transmission and reception behaviour. Simple and easy APIs allow users to inject packets/errors at any layer level.

#### **RC and EP Operation**

As RC or EP the BFM can generate Memory Messages, IO, and Config as requester or completer. In RC mode, the BFM is able to generate I/O and config requests. It can be configured as a loopback master. In EP mode, the BFM supports automatic responses to all transaction types.

#### **PCIe Interface Inspector**

The Interface Inspector tracks the traffic of the link and provides protocol-checking capability. Checks are configurable. They can be enabled and disabled individually for a particular test. It generates LOG file and displays protocol specific and transaction information. The log file can be tailored by the user depending on the requirement. Various verbosity levels are supported for warning, debug, errors and log.

The Genie-PCIe Interface Inspector checker provides protocol-checking capability with the following built-in rules:

- Endpoint rules

- Root Complex Integrated Endpoint Rules

- TLPs with Data Payloads Rules

- Routing and Addressing Rules

- First/Last DW Byte Enables Rules

- Memory, I/O & Configuration Request Rules

- Message Request Rules

- Completion Rules

- Request Handling Rules

- Completion Handling Rules

- Transaction Ordering Rules

#### BENEFITS

| ** | Guarantees compliance to PCIe 2.0 specification | * | Reduces test development effort                      |

|----|-------------------------------------------------|---|------------------------------------------------------|

| ** | Block level and System level verification       | * | Shortens verification schedule                       |

| *  | Reduces overall design and verification costs   | * | Plug-and-play into all major simulation environments |

# SUPPORTED SIMULATORS: ALDEC CADENCE MENTOR SYNOPSYS

| PCIe 2.0 COMPLIANCE SUITE                                                                                                                                                                                                                                             | PCIe 2.0 SOLUTIONS                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Developed by PerfectVIPs, the compliance suite is<br>a PCI-SIG based compliance test with additional<br>compliance coverage from checklists.                                                                                                                          | Developed by PerfectVIPs to address different system level PCIe architectures, the following PCIe solutions are available:                                                                   |

| <ul> <li>Verifies all layers of PCIe designs</li> <li>Provides comprehensive design coverage targeted at Phy, Datalink, Transaction &amp; Configuration Space</li> <li>Identifies all protocol violations</li> <li>Provides detailed reports on functional</li> </ul> | Verification IP:<br>PCIe 2.0 Root Complex (RC) VIP<br>PCIe 2.0 End Point (EP) VIP<br>PCIe 2.0 RC/EP VIP (configurable)<br>PCIe 2.0 RC Interface Inspector<br>PCIe 2.0 EP Interface Inspector |

| <ul> <li>coverage</li> <li>Provides directed and constrained random regression testing capability</li> <li>Developed with actual customer designs</li> </ul>                                                                                                          | Compliance Suites:<br>RC Compliance Test Suite<br>EP Compliance Test Suite                                                                                                                   |

PerfectVIPs Inc. 1762 Technology Drive, Suite 224, San Jose, CA 95110 T: 408 912 2316 F: 408 748 8838 E: sales@perfectvips.com For more information visit www.perfectvips.com